Synopsys Introduces Software-Defined Hardware-Assisted Verification to Enable AI Proliferation

New product capabilities deliver leading performance, capacity, and industry-first hardware-assisted test-automation capabilities to accelerate AI silicon innovation from data center to edge

Key Highlights

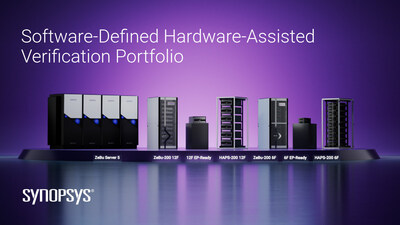

- Software-defined approach enables an up to 2x performance boost for ZeBu Server 5 and scales capacity up to 2x with modular HAV for AI-era mega designs

- New HAPS-200 12 FPGA and ZeBu-200 12 FPGA platforms for mainstream designs feature EP‑Ready Hardware that extends emulation and prototyping capacity by 2x and delivers leading performance for emulation and prototyping use cases

- New, industry-first hardware-assisted test automation capabilities enable faster, earlier detection of cache‑coherency and subsystem‑level bugs for maximum coverage

AI chip verification complexity is escalating rapidly as large language models continue to double in size roughly every four months, and interface data rates advance at a 2x rate every three years. Simultaneously, edge AI architectures are driving aggressive throughput, latency, and power‑efficiency targets that further expand the design and validation workload. To keep pace, the industry requires HAV solutions to support broader application coverage and run quadrillions of verification cycles, enabling first‑time‑right silicon and a seamless ability to integrate heterogeneous AI systems.

"As AI-driven systems become more complex, verification must scale just as quickly. Hardware-assisted verification is no longer optional. It is critical to meeting aggressive time-to-market goals and ensuring silicon readiness," said

"As AI becomes more pervasive across almost every industry and products are now workload-optimized and silicon-powered, building high confidence early that the workloads are running to spec on the silicon under development is critical," said

The latest advancements across

Breakthrough performance and capacity for the AI era: The latest software-defined updates and modular HAV are available across the ZeBu and HAPS platforms. Of note, with these updates, the industry's highest capacity-scalable emulation platform, ZeBu Server 5, supports complex designs to meet the demands of mega designs supporting data center AI training and inference, GPU, custom accelerators, and networking IPU/DPU workloads. Modular HAV for HAPS enables the largest prototypes for software development, with further improvements for compute, storage, and bring-up capabilities.

New HAPS and ZeBu platforms: The new HAPS-200 12 FPGA and ZeBu-200 12 FPGA systems address the complexity and high-performance requirements for data center-sub-system, mobile, client, server, consumer, and edge AI applications. They deliver 2x higher capacity compared to previous 6 FPGA platforms utilizing the flagship AMD Versal™ Premium VP1902 adaptive SoCs, offering EP-Ready Hardware-enabled configurability between prototyping and emulation.

"As NVIDIA's AI platforms have become software‑defined to meet rising performance and scalability demands, verification must evolve in the same way," said

Software-defined HAV capabilities extend system lifetime value: Continuous software improvements deliver compounding performance gains, increased debug productivity, as well as additional use case capabilities for both new and installed systems. The Synopsys HAV portfolio supports new, industry-first Hardware-Assisted Test Solutions, test automation capabilities that allow teams to stress corner cases for processor, memory, and I/O subsystems as well as full-system coherency validation and observe system behavior under realistic workloads in emulation long before silicon is ready. For mixed-signal and system-level designs, Real-Number Models (RNM) emulation enables fast, scalable abstraction of analog behavior within digital-centric verification flows for faster software bring-up. For safety-critical and high-reliability designs, new fault emulation capabilities enable scalable fault injection and analysis across RTL simulation, emulation, and prototyping.

"Verifying hardware for our highly anticipated rack-scale AMD Helios solution – marked by massive AI scale, complex subsystems, and robust software stacks – demands scalable and versatile verification platforms," said

Availability & Additional Resources

Software-defined enhancements are being rolled out continuously across the HAV portfolio, with the new capabilities available to users today. The new EP‑Ready HAPS-200 12 FPGA and ZeBu-200 12 FPGA platforms are available today and in Q3 2026, respectively. HAPS-200 1 FPGA platform is available today.

- Product Page: Synopsys HAV Solutions Family

- Blog: Introducing Software-Defined Hardware-Assisted Verification: A New Benchmark for AI-Era Chip Design

- Video: Software-Defined Hardware-Assisted Verification for the AI Era

Follow Synopsys Converge 2026 News and Updates

Synopsys Converge is taking place

About

© 2026

Contacts

Media

corp-pr@synopsys.com

![]() View original content to download multimedia:https://www.prnewswire.com/news-releases/synopsys-introduces-software-defined-hardware-assisted-verification-to-enable-ai-proliferation-302711214.html

View original content to download multimedia:https://www.prnewswire.com/news-releases/synopsys-introduces-software-defined-hardware-assisted-verification-to-enable-ai-proliferation-302711214.html

SOURCE